一种FPGA实现的序列图像目标多维特征实时提取方法

doi: 10.11728/cjss2023.03.2022-0014 cstr: 32142.14.cjss2023.03.2022-0014

An FPGA-implemented Method for Real-time Multi-dimensional Feature Extraction of Sequence Image Targets

-

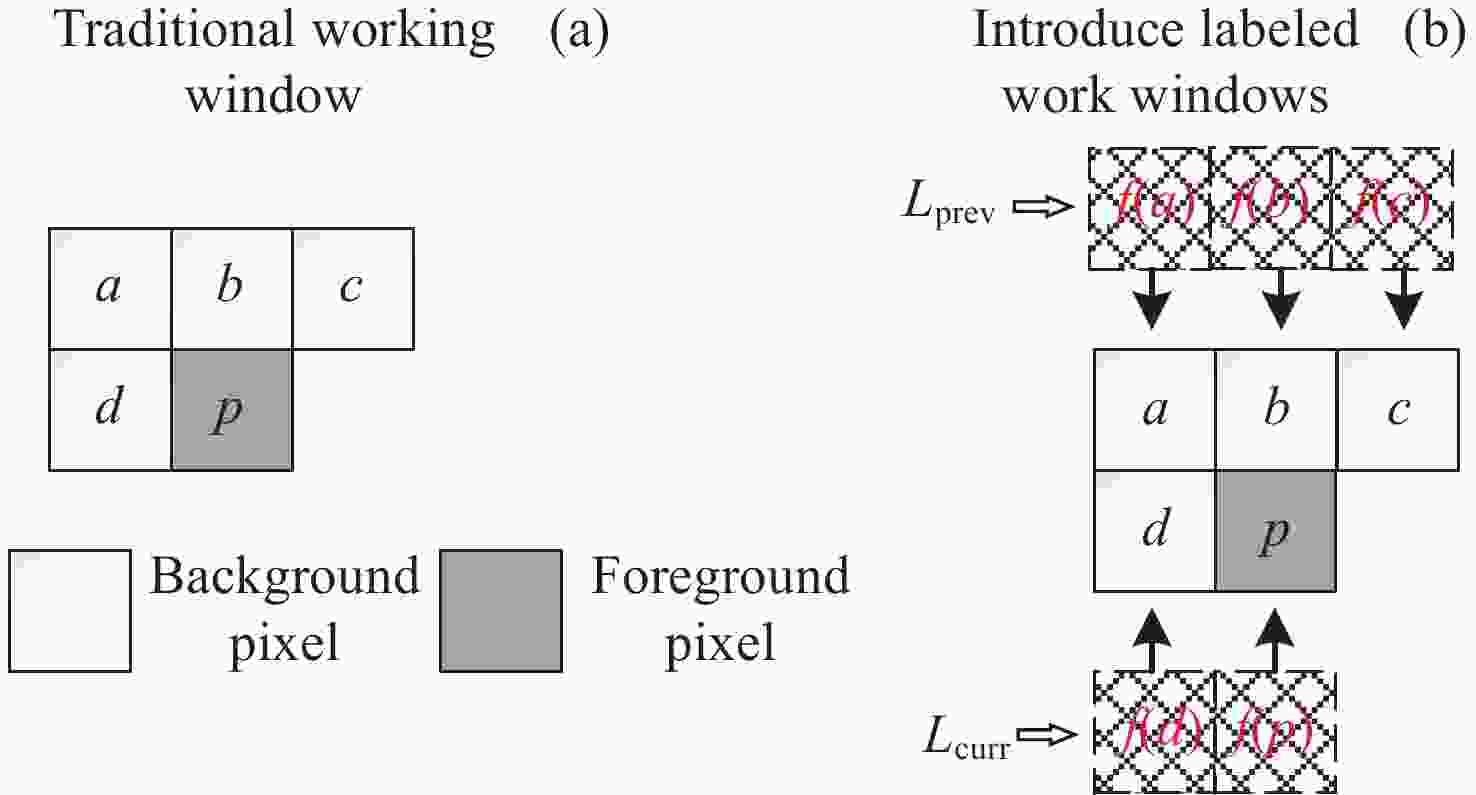

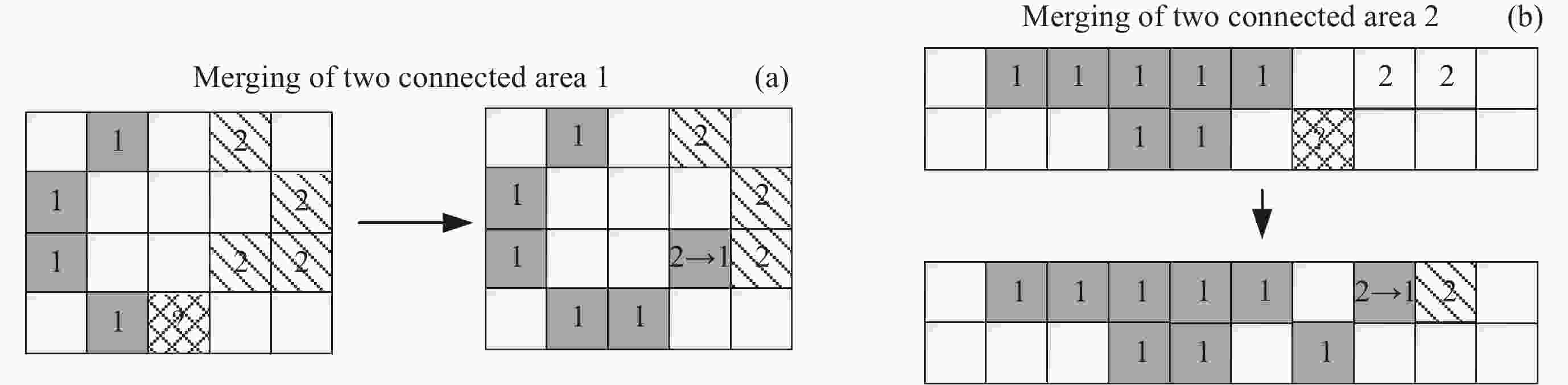

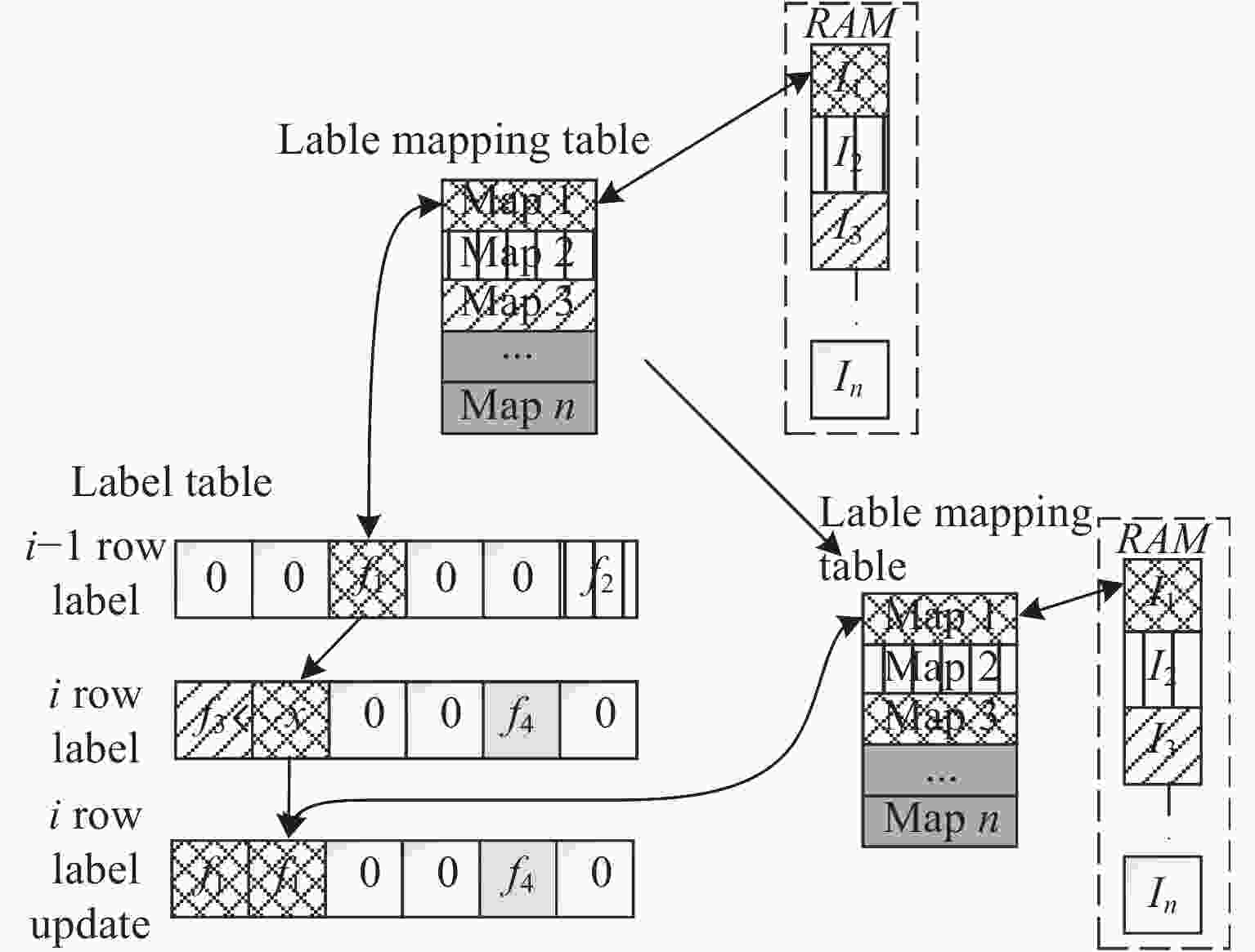

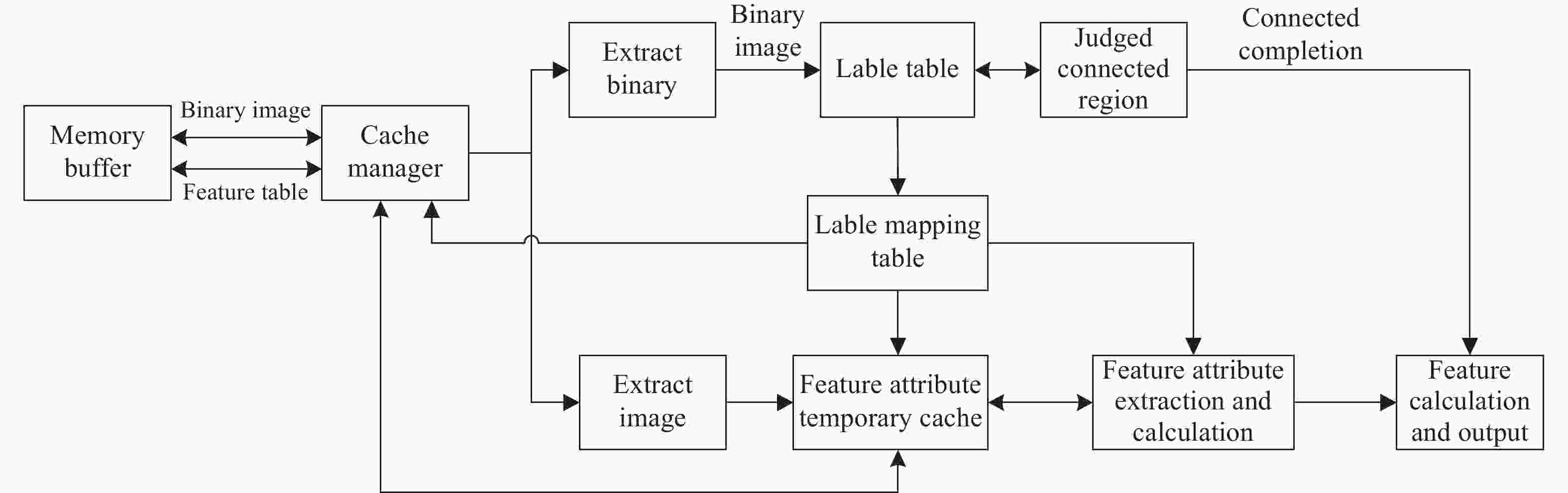

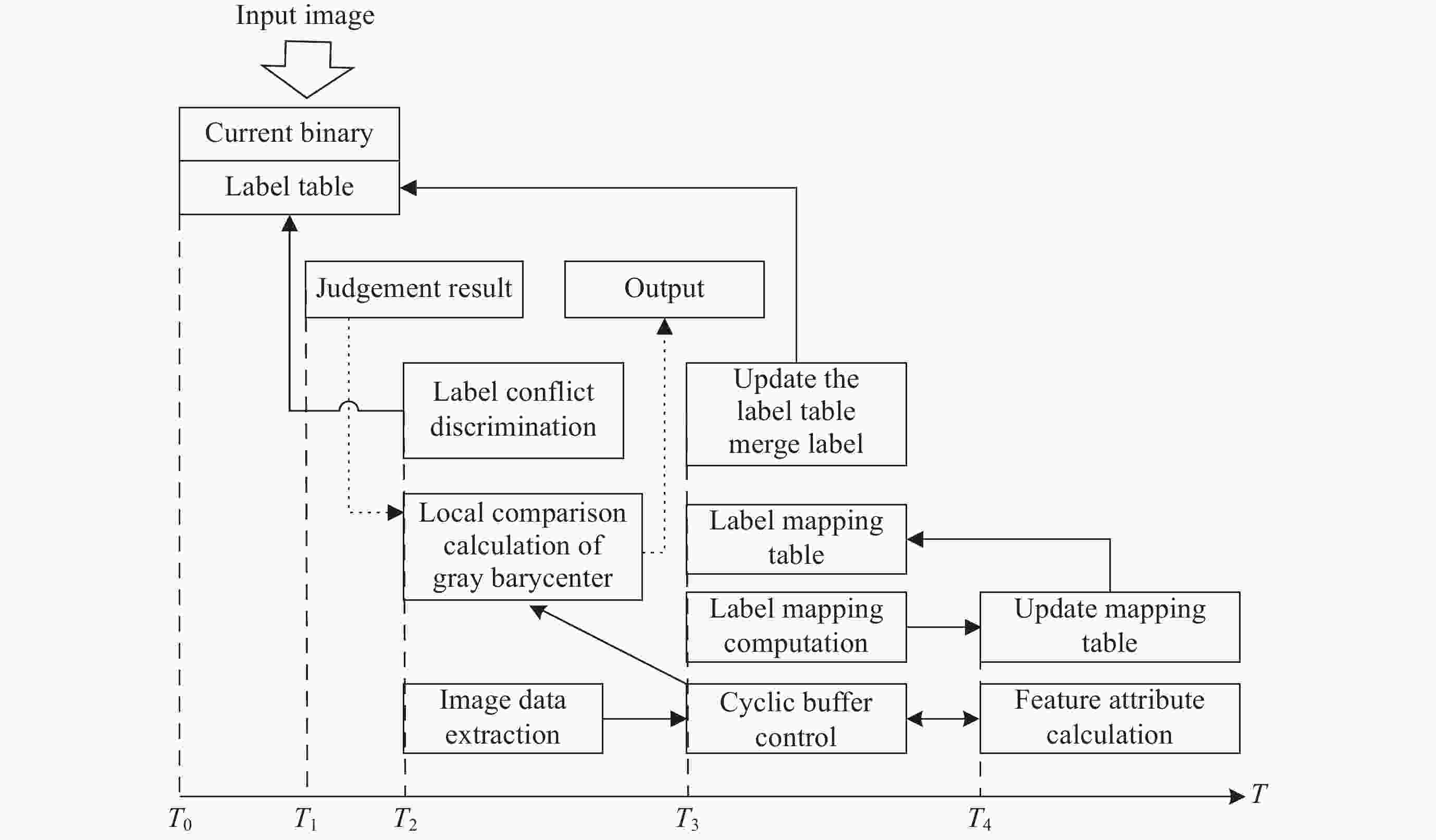

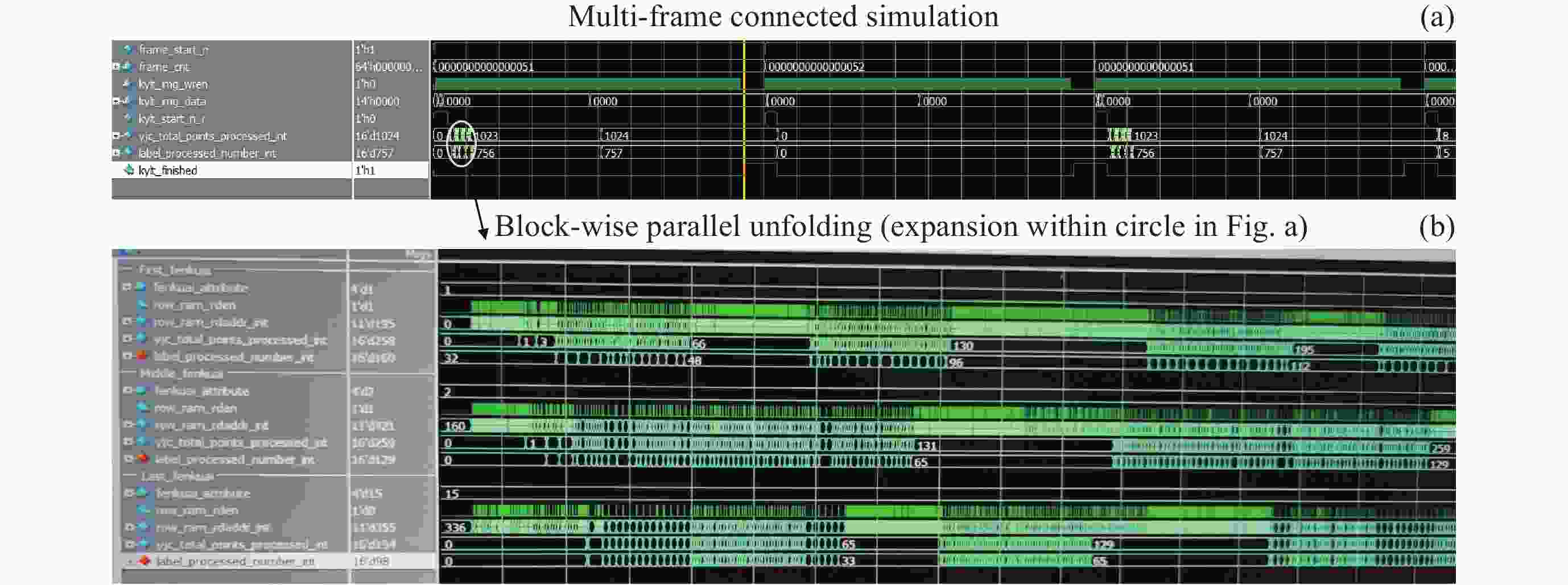

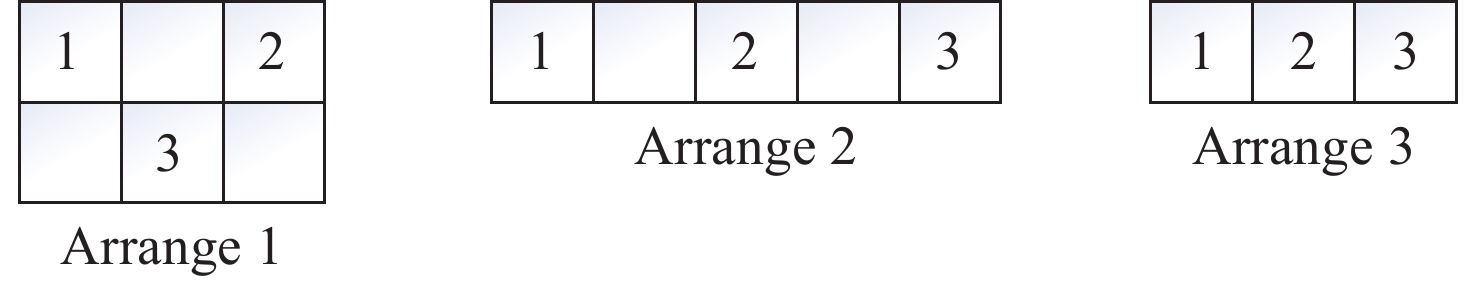

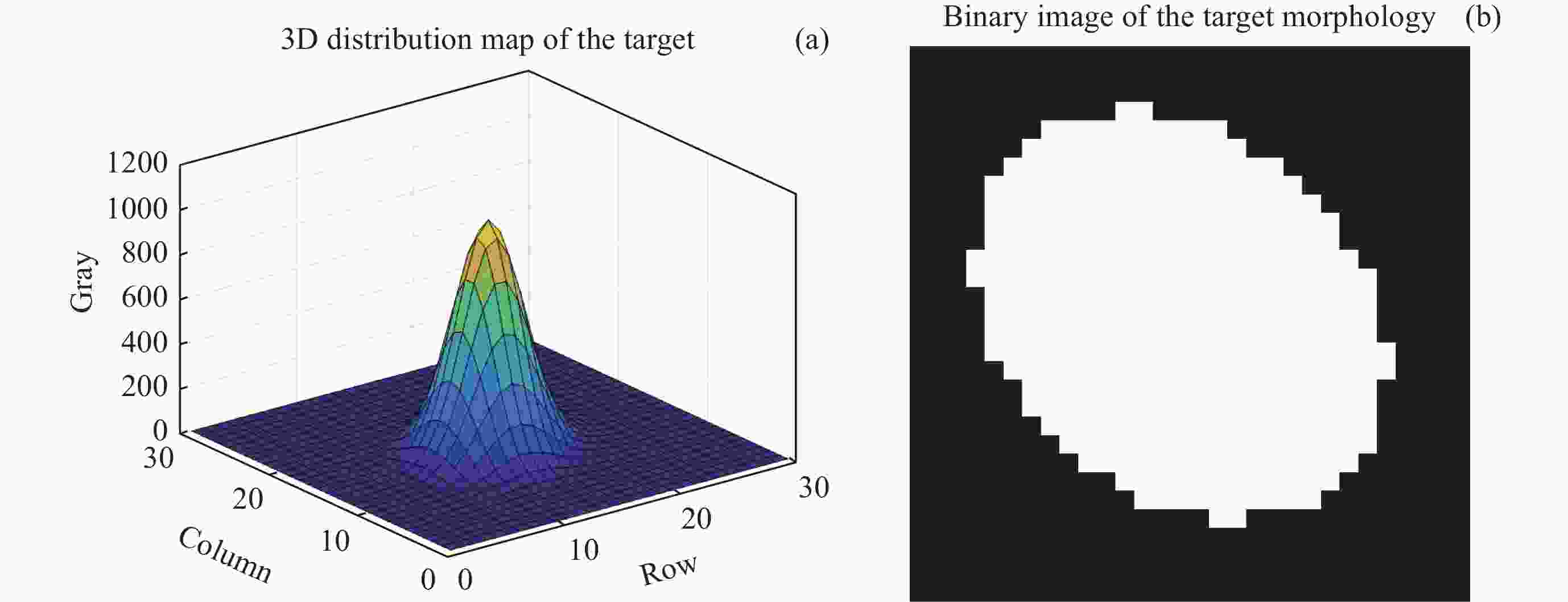

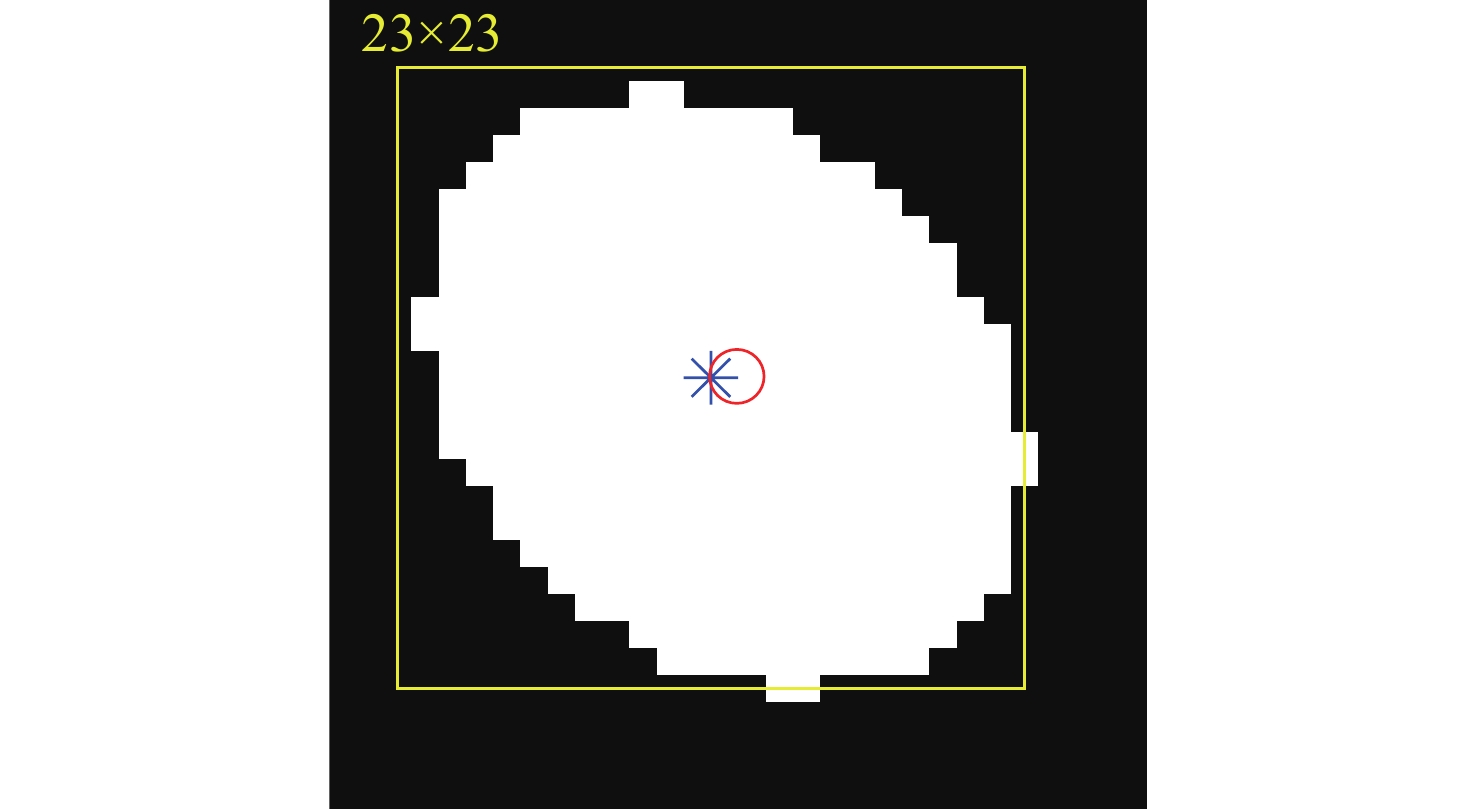

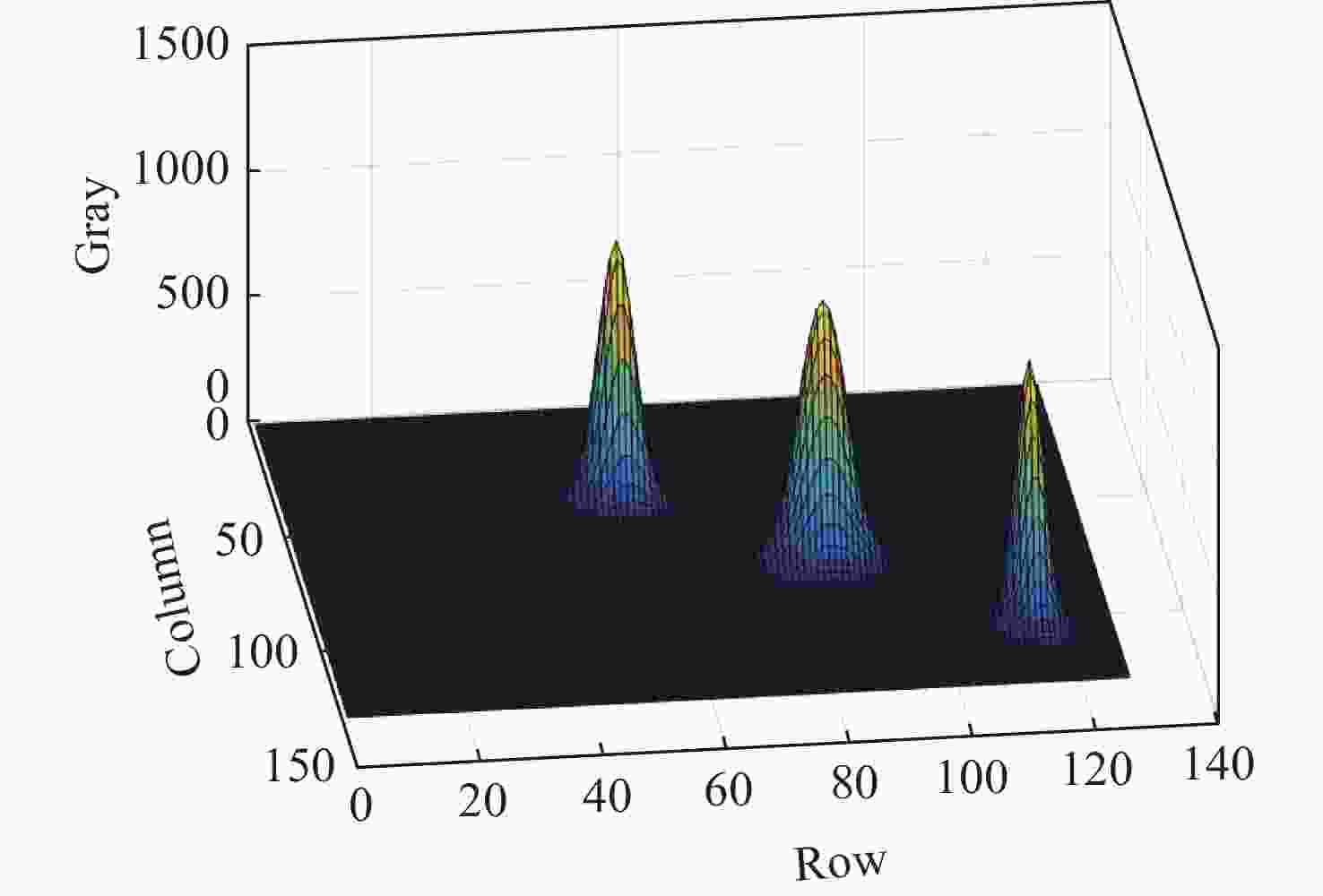

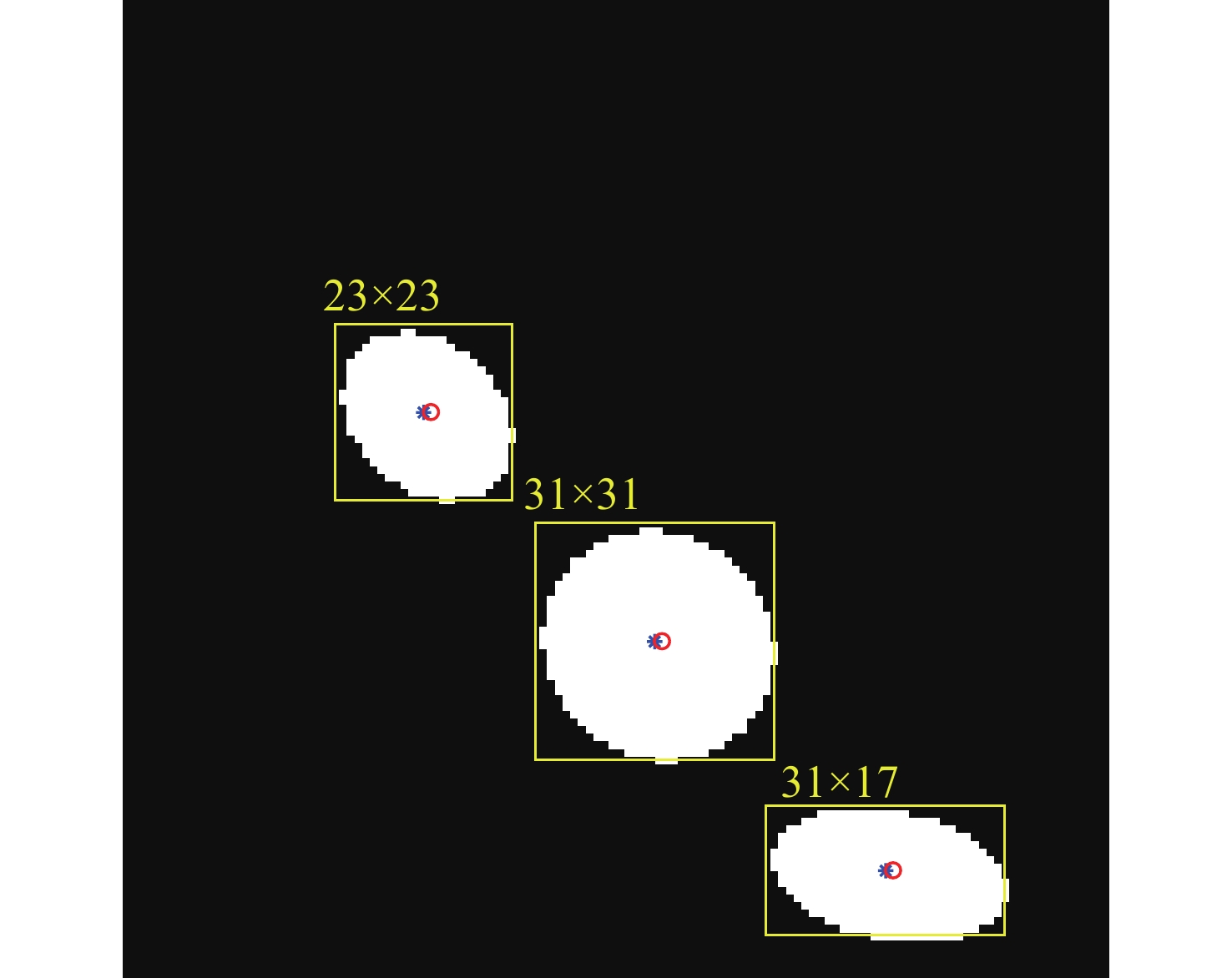

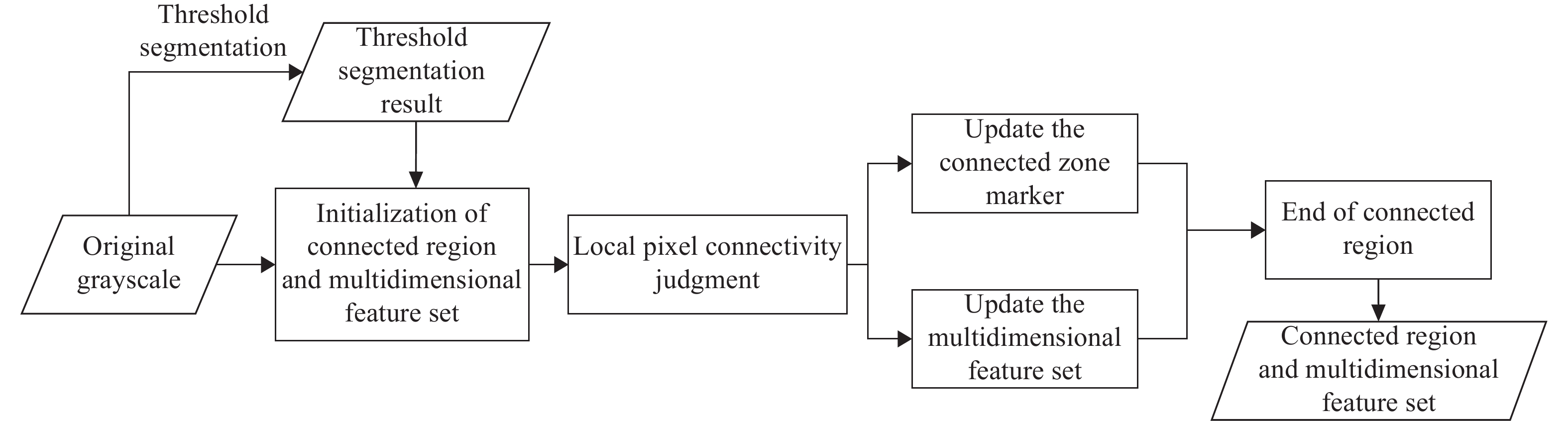

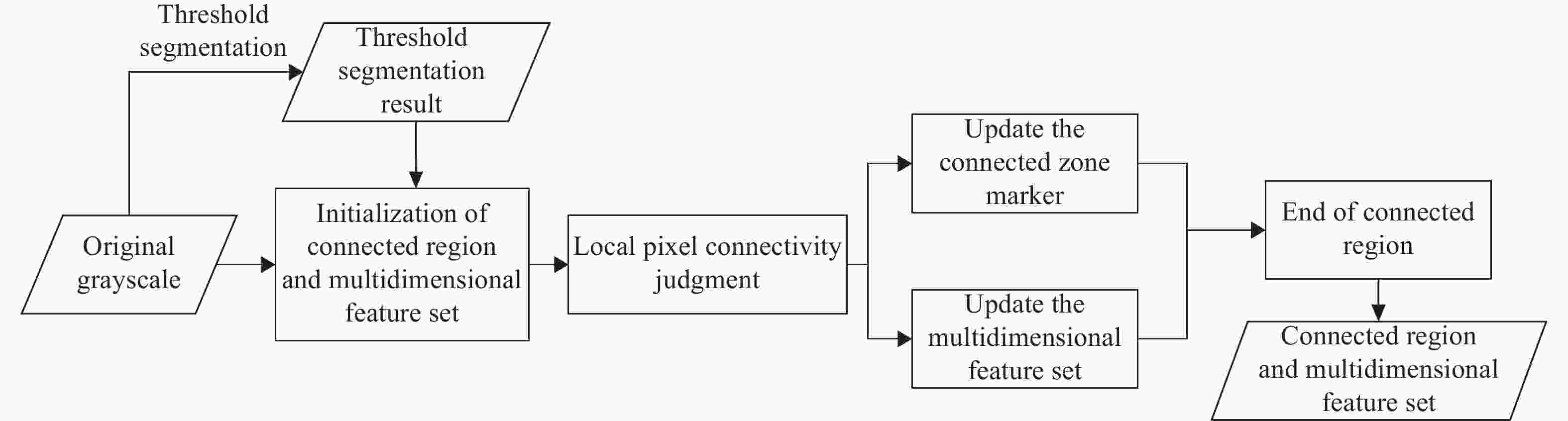

摘要: 目标区域多维特征的建模表征是实现目标跟踪搜索的前提。传统的特征提取方法通常先连通出目标区域,再计算目标特征,实时性不强。提出了一种基于像素的连通域标记及目标特征同步计算方法,建立特征传递机制,利用标号映射表关联标号表与特征属性表,并在区域邻接时进行标号合并和特征属性同步传递计算,保证了目标区域连通完成即可输出目标区域特征。给出一种基于FPGA硬件设计的实现方案。仿真测试结果显示,此方法具有以下几方面优势:连通域标记耗时少,仅为(L × W + 2n/m) × Tclk,接近理论最小值(L × W) × Tclk;利用循环缓存区存储图像,资源消耗小;标记与计算并行处理,提升了检测跟踪效率;多目标特征经测试验证结果准确,可有效支持后续的目标跟踪检测;具有理论与实用价值。Abstract: The prerequisite of target detection and tracking is to model and represent the target based on multi-dimensional features extracted from the target region. The traditional target feature extraction needs to connect the target region first and then must calculate the target feature, which has still room for improvement in real-time performance. An advantage of the new method based on the synchronous calculation of pixel-connected domain markers and target features is that the target features can be output when the target region is connected. This article proposes a method highlighting pixel-based marking of connection domains and synchronous computation of target features, which can output target features immediately after target areas are connected. By setting up a feature transfer mechanism, this method establishes a marker table, a marker mapping table and a feature attributes table while scanning images, and links the marker mapping table and the feature attributes table with the help of the marker table. When different areas are adjacent to one another, markers are consolidated while the features’ attributes are synchronously transferred and computed, ensuring real-time extraction of the target features. Regarding real-time and multiple-dimensional extraction of the features of multiple targets in high-resolution distant sensing images, the article proposes an implementation plan based on FPGA hardware design. According to the results of a number of simulation tests, the method featuring high-speed marking of connection domains over one iteration of split pixels and real-time computing of target features boasts the following outstanding characteristics: The time consumed by marking connection domains is only (L × W + 2n/m) × Tclk, close to the theoretical minimum (L × W) × Tclk; saving images in cyclical buffers only takes up few resources; parallel pipeline processing of marking and computation improves the detection and tracking efficiency; the test results of multiple target features are accurate and consequently can effectively support subsequent target tracing detections; and the method also has both theoretical and practical values.

-

Key words:

- Image processing /

- Target feature extraction /

- Connected domain marker /

- Real-time

-

表 1 目标区域多维特征属性信息

Table 1. Multi-dimensional feature attribute information of target region

行(x)最大坐标 列(y)最大坐标 行(x)最小坐标 列(y)最小坐标 能量峰值 区域点数和 区域能量和 峰值点局部灰度和 行(x)坐标灰度积累积和 列(y)坐标灰度积累积和 表 2 存储资源消耗

Table 2. Storage resource

内容 存储区域 数量 二值+原图 Block RAM 4 目标特征属性集 Block RAM 14 标号表 Block RAM 2 标号映射表 Block RAM 1 表 3 单目标仿真参数

Table 3. Single objective simulation parameters

序号 参数名称 含义 设置值 1 峰值点坐标 目标能量峰值点图像坐标 ${\mu _x} = 15$

${\mu _y} = 15$2 协方差矩阵C 用于描述形态分布 [8, 2; 2, 8] 表 4 多目标仿真参数

Table 4. Multi-objective simulation parameters

序号 参数名称 含义 设置值 目标1 峰值点坐标 目标能量峰值点图像坐标 (40, 65) 协方差矩阵C 用于描述形态分布 [8, 2; 2, 8] 目标2 峰值点坐标 目标能量峰值点图像坐标 (70, 85) 协方差矩阵C 用于描述形态分布 [5, 2; 2, 5] 目标3 峰值点坐标 目标能量峰值点图像坐标 (100,115) 协方差矩阵C 用于描述形态分布 [8, 2; 2, 8] 表 5 多目标特征提取结果

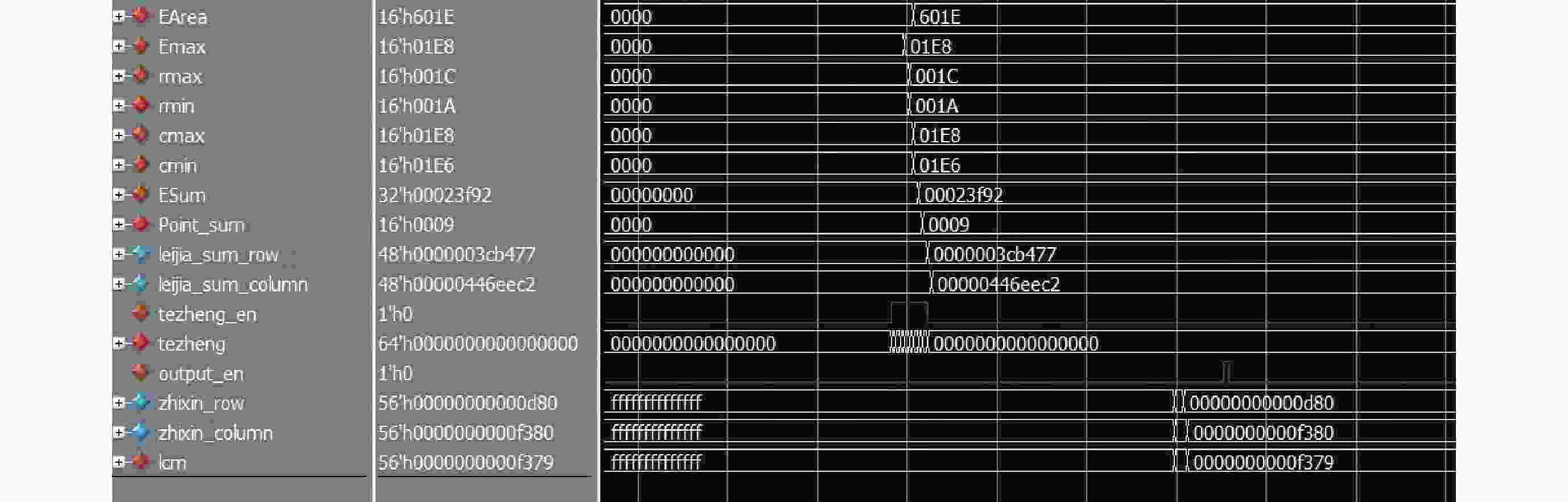

Table 5. Multi-target feature extraction results

序号 特征名称 目标1输出值 目标2输出值 目标3输出值 1 能量峰值 1023 800 500 2 能量峰值点坐标 (55, 40) (85, 70) (115, 100) 3 区域行列边界 [44 66 29 51] [71 99 56 84] [107 123 86 114] 4 能量和 49783 75204 26830 5 区域目标像素数 373 689 371 6 局部对比度 8.25 7.62 7.27 7 灰度重心坐标 (55, 41) (85, 71) (115, 101) -

[1] ROSENFELD A, PFALTZ J L. Sequential operations in digital picture processing[J]. Journal of the ACM, 1966, 13(4): 471-494 doi: 10.1145/321356.321357 [2] WANG Fan, ZHOU Guoqing, ZHANG Rongting, et al. FPGA-oriented fast connected component labeling method[J]. Computer Engineering and Applications, 2020, 56(22): 230-235 doi: 10.3778/j.issn.1002-8331.1909-0222 [3] LING Luxiang. Target Localization Method Based on Embedded Vision with FPGAs and Its Application[D]. Guangzhou: South China University of Technology, 2017 [4] ZHANG Guohe, XU Kuai, DUAN Guodong, et al. A fast labeling algorithm of connected components applicable for hardware implementation[J]. Journal of Xi’an Jiaotong University, 2018, 52(8): 95-101 doi: 10.7652/xjtuxb201808015 [5] DAI Huadong, HU Moufa, LU Huanzhang, et al. Design and implementation of target detection algorithm based on connected-domain labeling[J]. Modern Electronics Technique, 2015, 38(20): 71-74 doi: 10.3969/j.issn.1004-373X.2015.20.019 [6] ZHAO Xiao. Speed-up of Connected Component Labeling Algorithm and Its Application in Paper Defect Detection[D]. Xi’an: Shaanxi University of Science and Technology, 2019 [7] YU Xiaoyu. Research on the Technologies of High Speed Vision Measurement System[D]. Harbin: Harbin Institute of Technology, 2014 [8] FENG Haiwen, NIU Lianqiang, LIU Xiaoming. Efficient one-scan algorithm for labeling connected component[J]. Computer Engineering and Applications, 2014, 50(23): 31-35 [9] PANDEY J G, KARMAKAR A, MISHRA A K, et al. Implementation of an improved connected component labeling algorithm using FPGA-based platform[C]//Proceedings of 2014 International Conference on Signal Processing and Communications. Bangalore: IEEE, 2014: 1-6 [10] TAN Xubin, XIE Yizhuang, CHEN He, et al. Design and implementation of the connected component labeling based on FPGA[J]. Signal Processing, 2011, 27(11): 1729-1733 doi: 10.3969/j.issn.1003-0530.2011.11.018 [11] FAN Qiaoyun, ZHANG Guangjun. Spot centroiding algorithm for discrete noise image and its hardware implementation[J]. Optics and Precision Engineering, 2011, 19(12): 2992-2998 doi: 10.3788/OPE.20111912.2992 -

-

下载:

下载: