Design and Implementation of a High-performance Image Compression Core for Spaceborne Applications

-

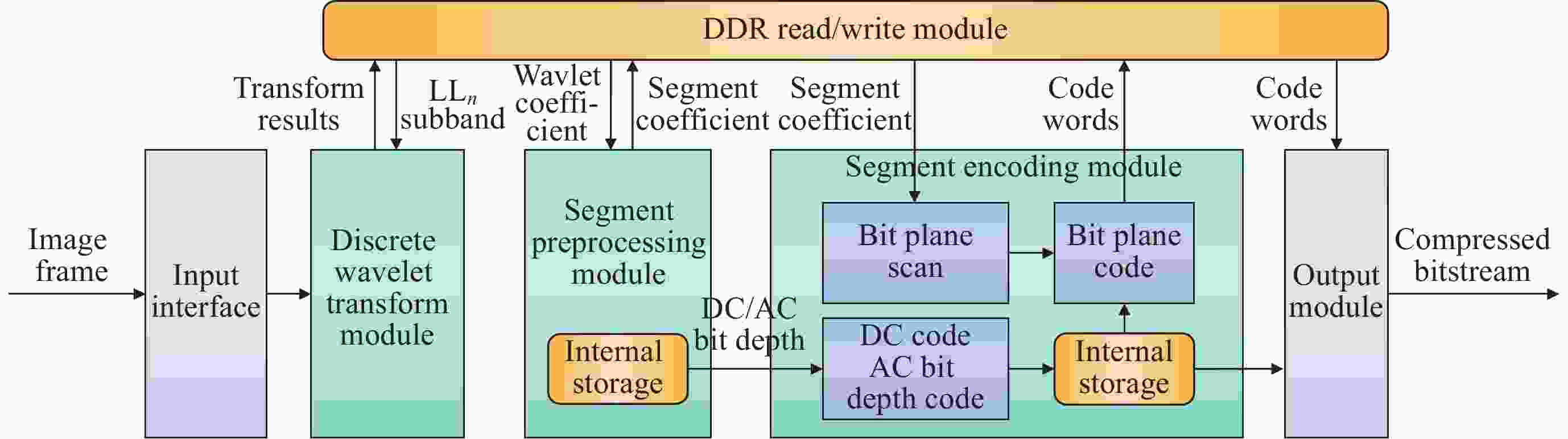

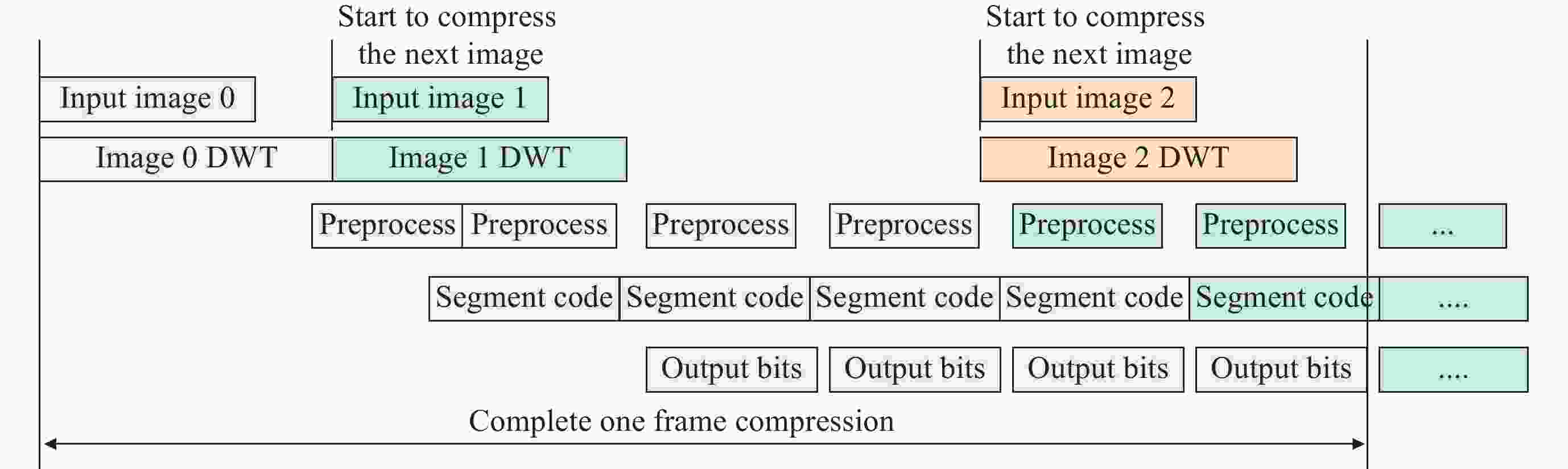

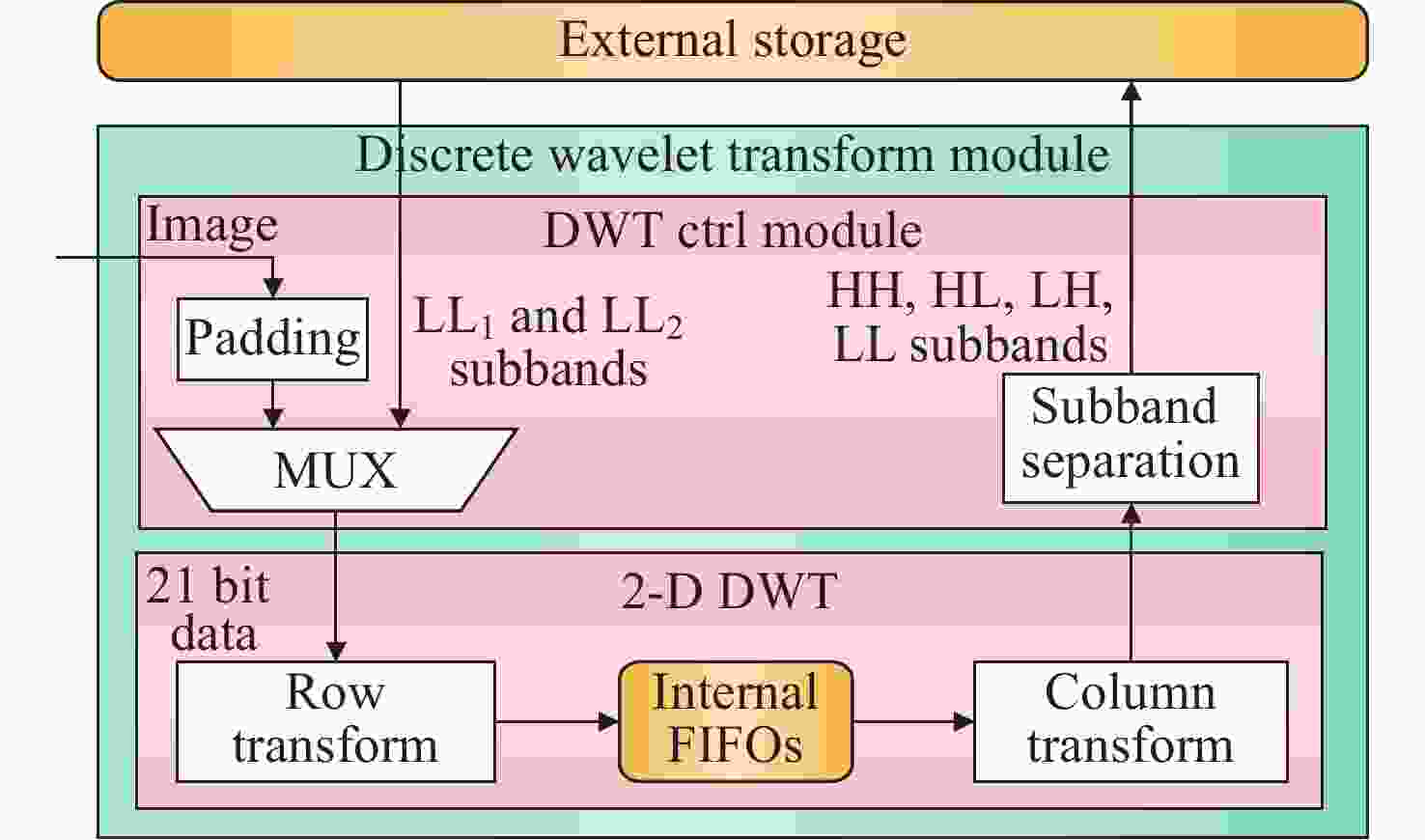

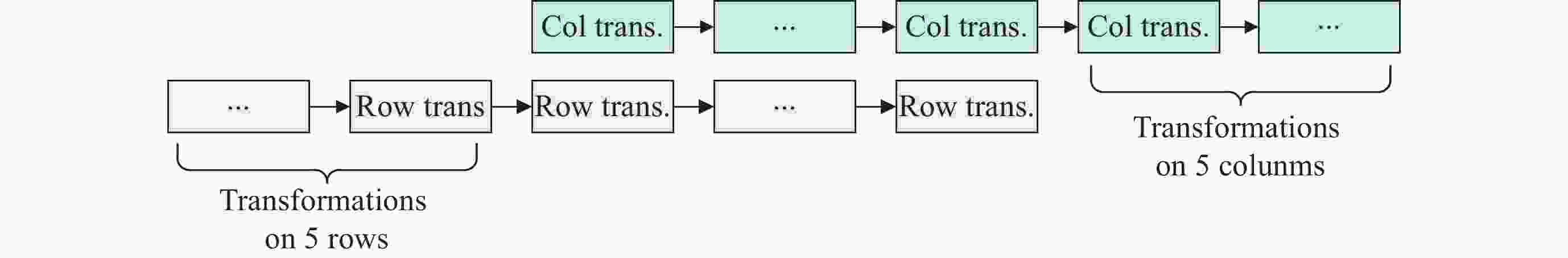

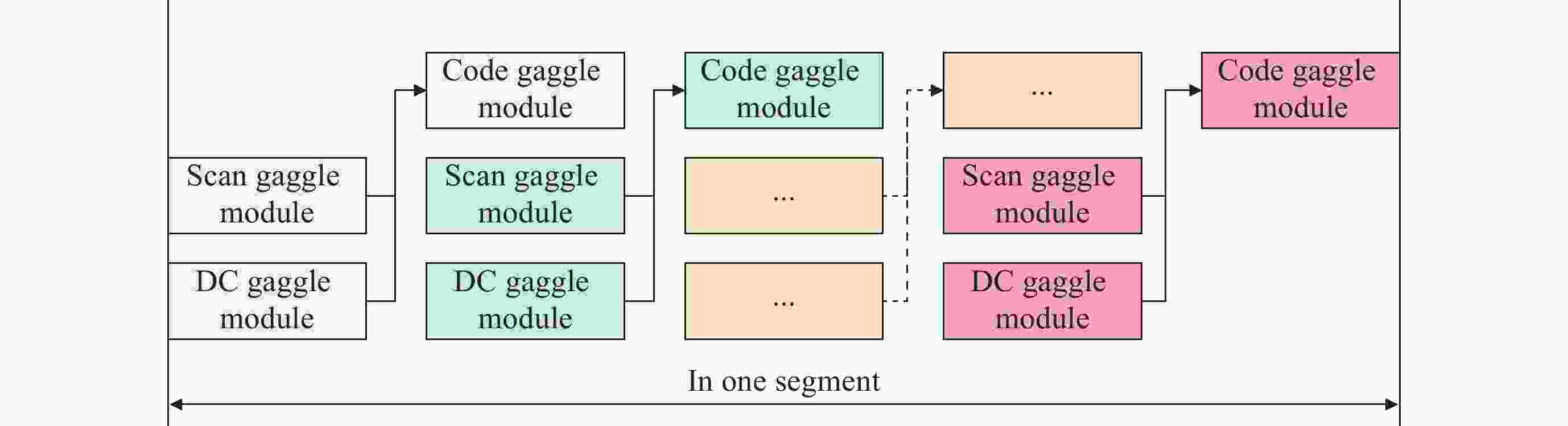

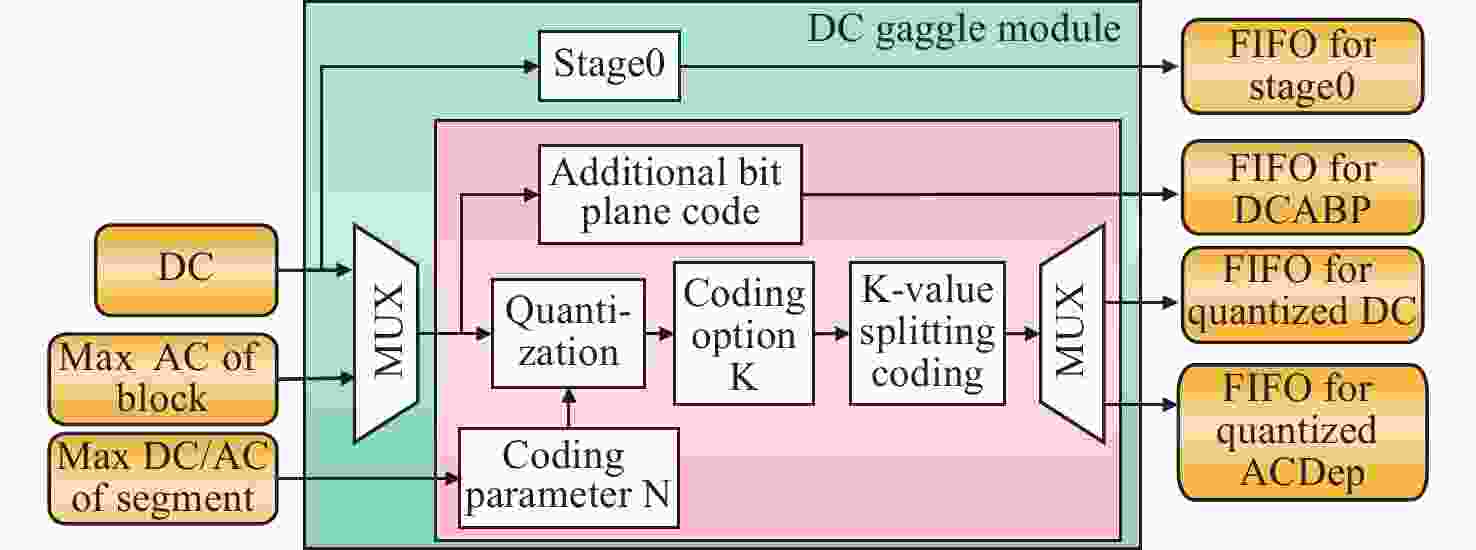

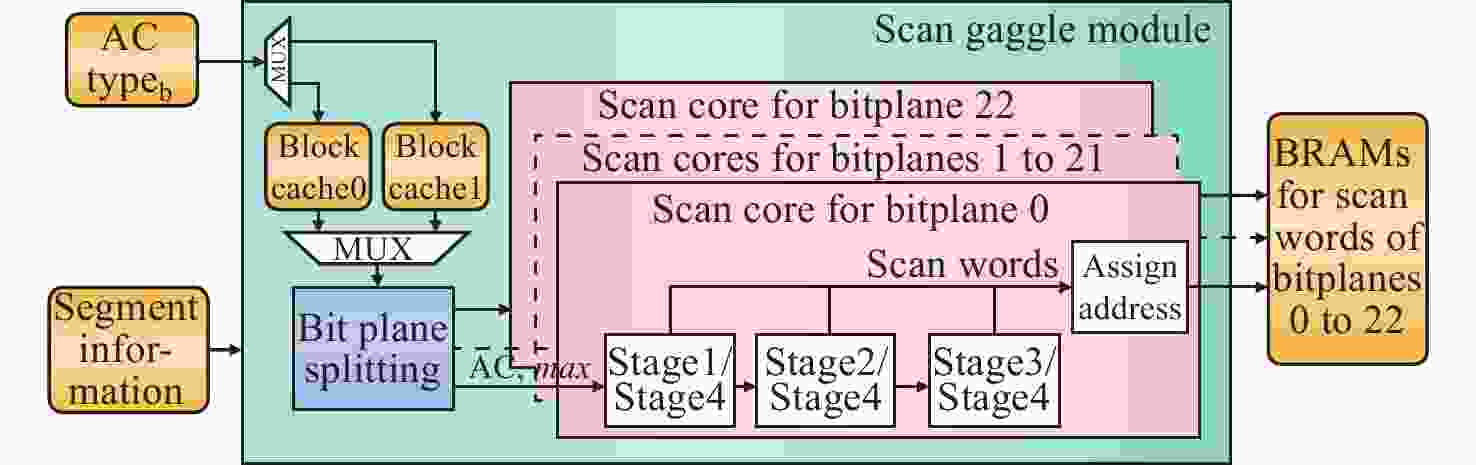

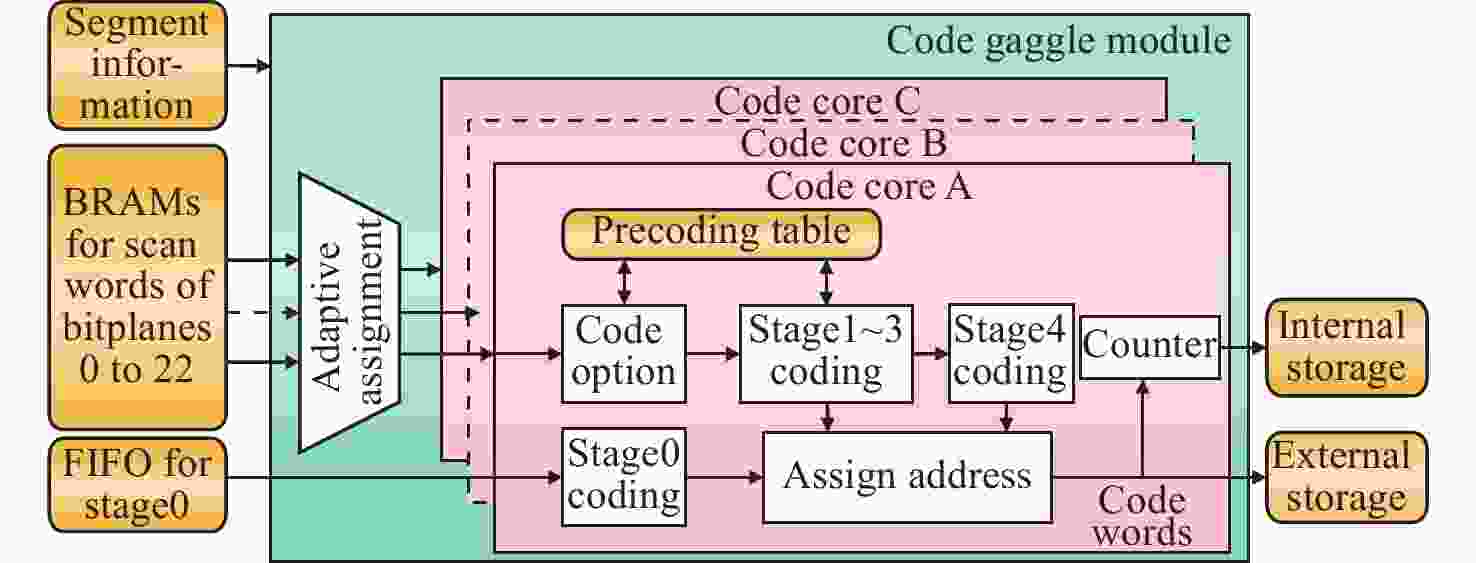

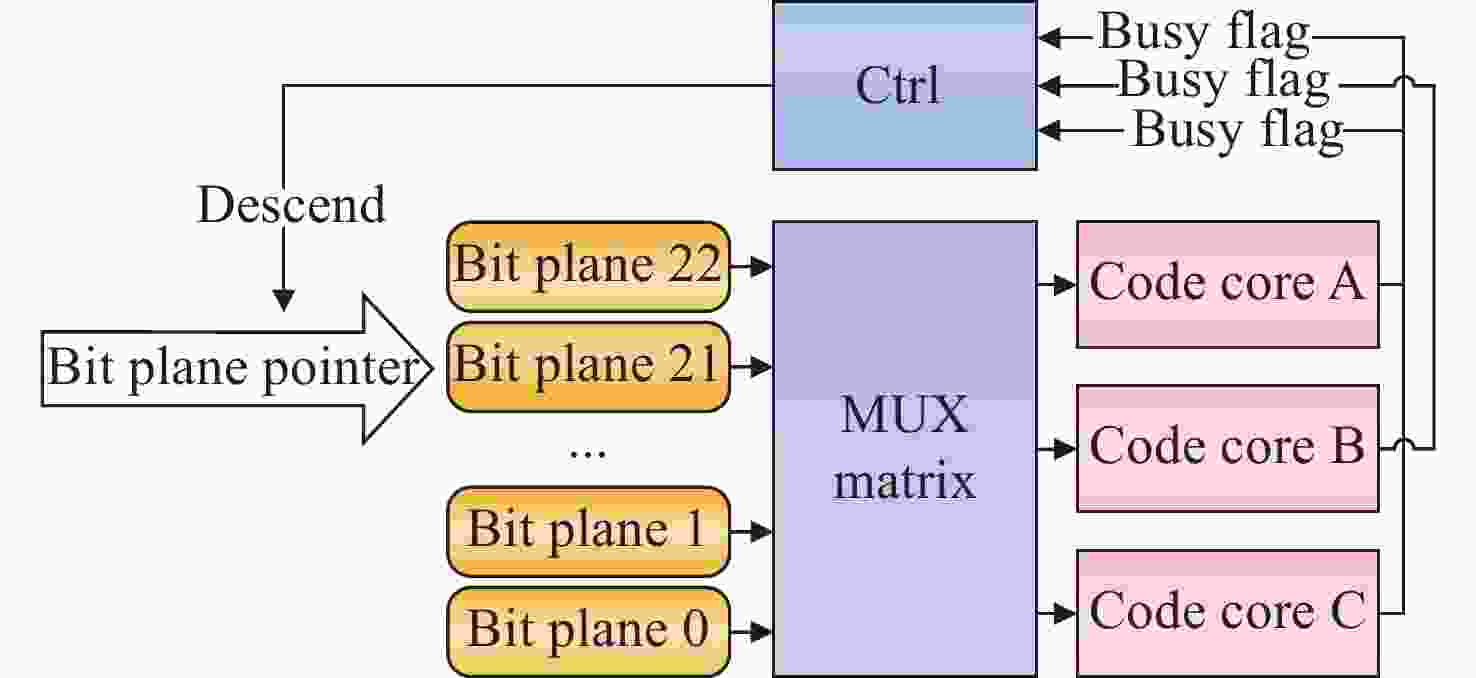

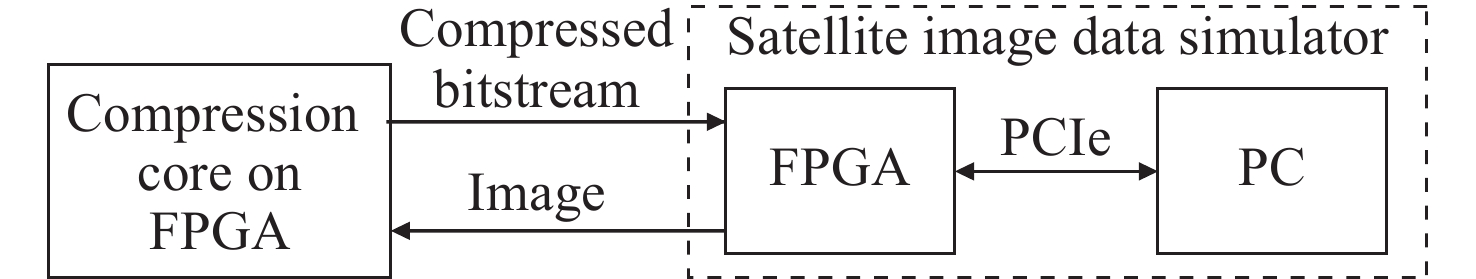

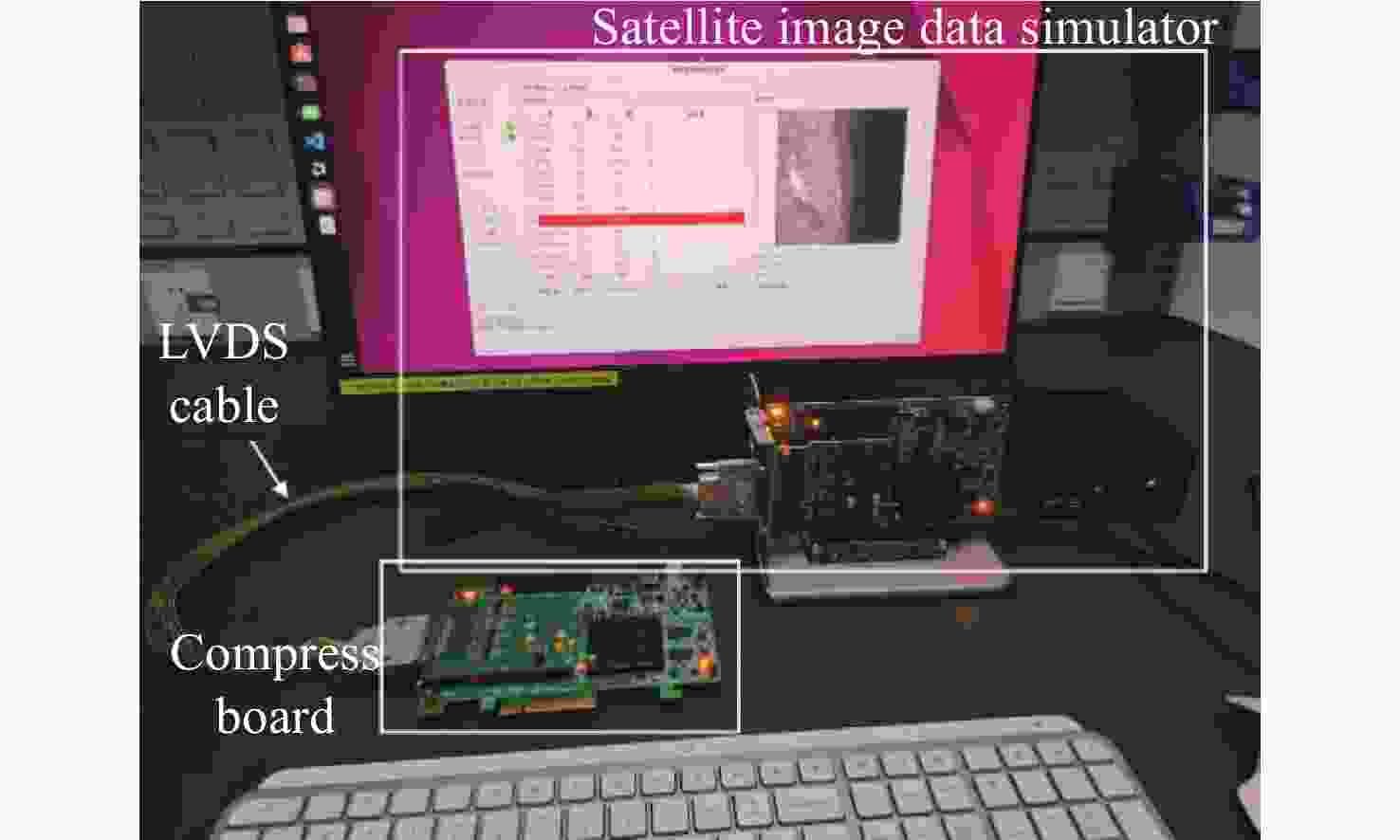

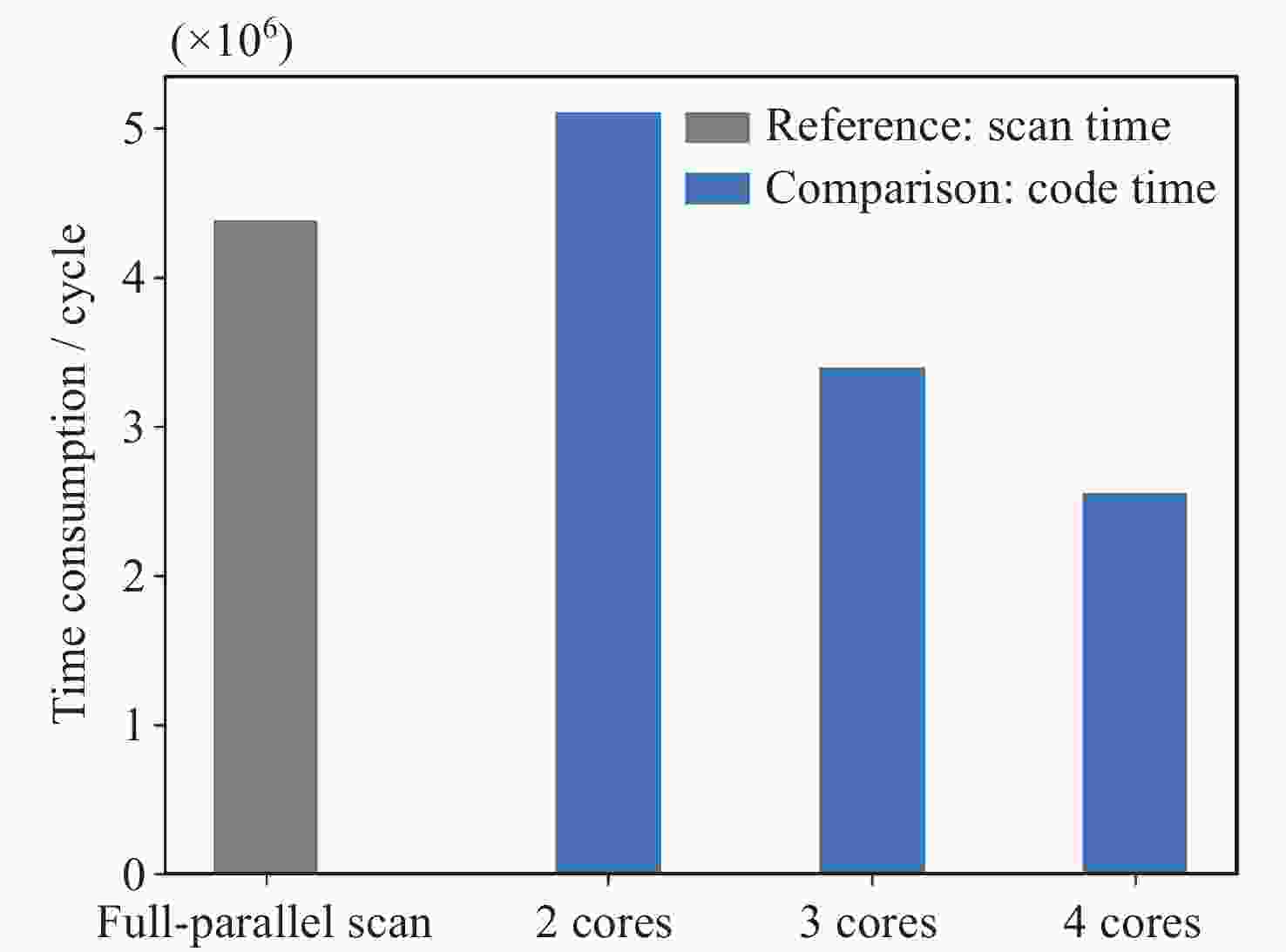

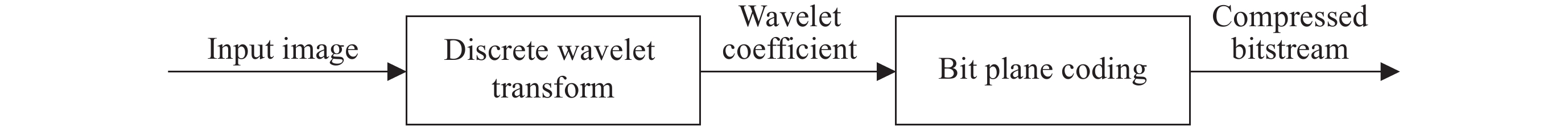

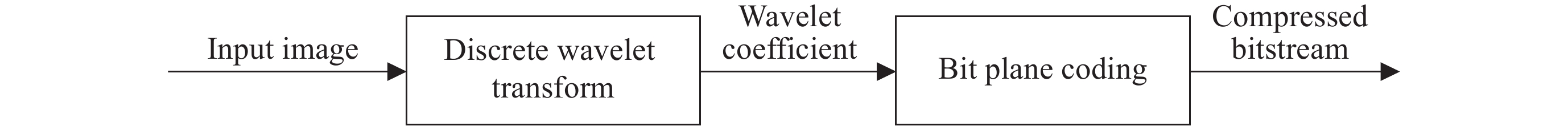

摘要: 为了满足航天应用中图像数据高效存储与传输的需求, 基于FPGA设计并实现了一种符合CCSDS 122.0-B-1标准的星载高性能图像压缩核. 充分考虑算法特性与实现平台特点, 设计了新颖的编码控制逻辑与数据组织结构. 针对压缩效率这一关键指标, 设计了段大小为256的算法实现架构, 压缩效率处于同类应用前列. 通过分段压缩机制, 有效防止了误码扩散, 并支持压缩质量连续调节与图像渐进传输. 针对扫描与编码环节的性能瓶颈, 提出了全并行扫描及动态优化并行编码方法, 实测编码效率提高约50%. 压缩核支持图像最大尺寸4096×4096 pixel, 最大位深度16 bit. 通过实际测试, 压缩核吞吐率可达90.64 ×106 sample·s–1, 可满足大部分航天任务的图像压缩需求.Abstract: To address the critical need for efficient image storage and transmission in aerospace applications, this study presents a CCSDS 122.0-B-1-compliant compression core implemented on FPGA. The design incorporates innovative encoding control logic and optimized data organization through co-optimization of algorithmic features and hardware constraints. A segment-based architecture with 256-pixel blocks achieves superior compression efficiency among existing solutions, while effectively containing error propagation through segmented compression. The architecture further enables continuous quality adaptation and progressive image transmission. To resolve performance bottlenecks in scanning and encoding processes, fully parallelized scanning with adaptive parallel encoding was developed, and a 50% efficiency improvement was demonstrated in validation tests. Supporting images up to 4096×4096 pixel with 16-bit depth, the core delivers 90.64×106 sample·s–1 throughput, meeting operational requirements for diverse space missions.

-

Key words:

- Image compression /

- FPGA /

- CCSDS /

- Wavelet transform /

- Bit-plane encoding

-

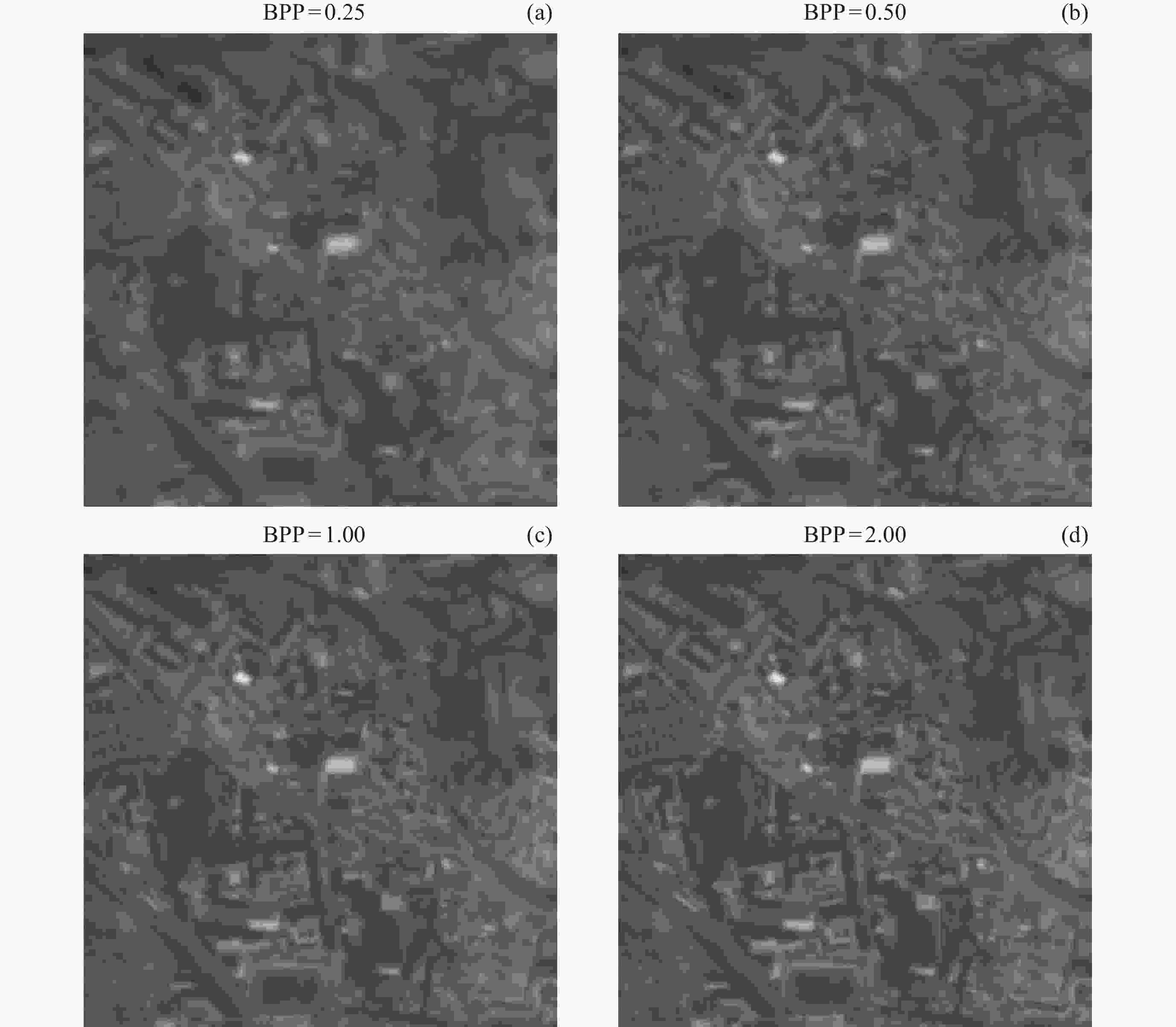

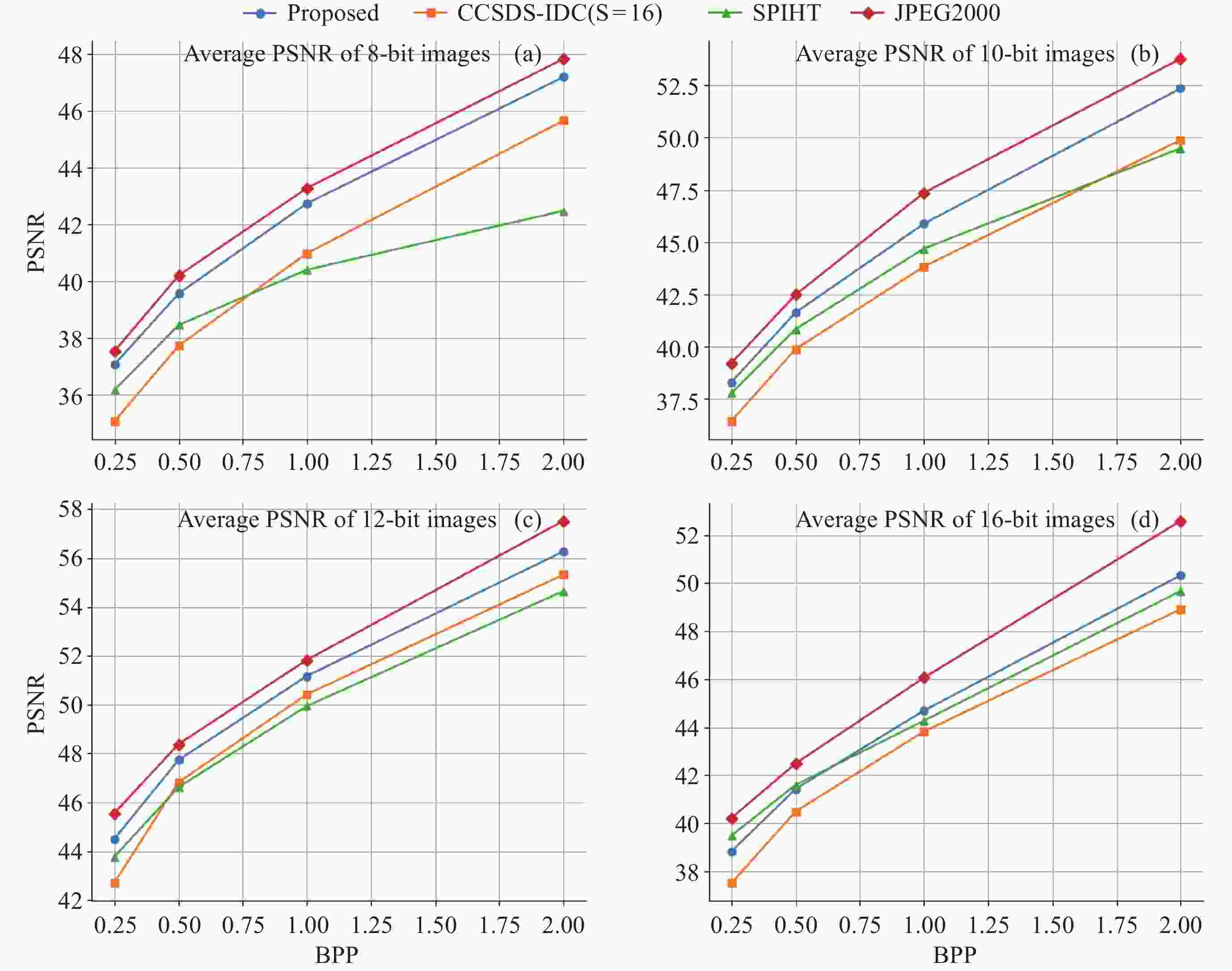

表 1 不同目标比特率下压缩图像的PSNR值(单位: dB)

Table 1. PSNR values of compressed images at different target BPP (Unit: dB)

图像名称 位深度/bit BPP=0.25 BPP=0.50 BPP=1.00 BPP=2.00 b1 8 40.35 42.59 45.20 48.90 b2 8 40.34 42.84 45.73 49.75 lunar 8 27.64 30.68 35.07 41.10 ocean_2 kb1 10 36.03 39.42 43.89 50.71 landesV_G7_10 b 10 40.98 42.88 45.70 51.88 marseille_G6_10 b 10 28.35 31.53 35.35 41.55 solar 12 41.92 45.01 48.73 54.67 sun_spot 12 48.97 52.61 55.50 59.68 sar16 bit 16 47.64 49.76 52.88 58.50 p160_b_f 16 30.02 33.09 36.50 42.13 表 2 测试图像段编码耗时及吞吐率

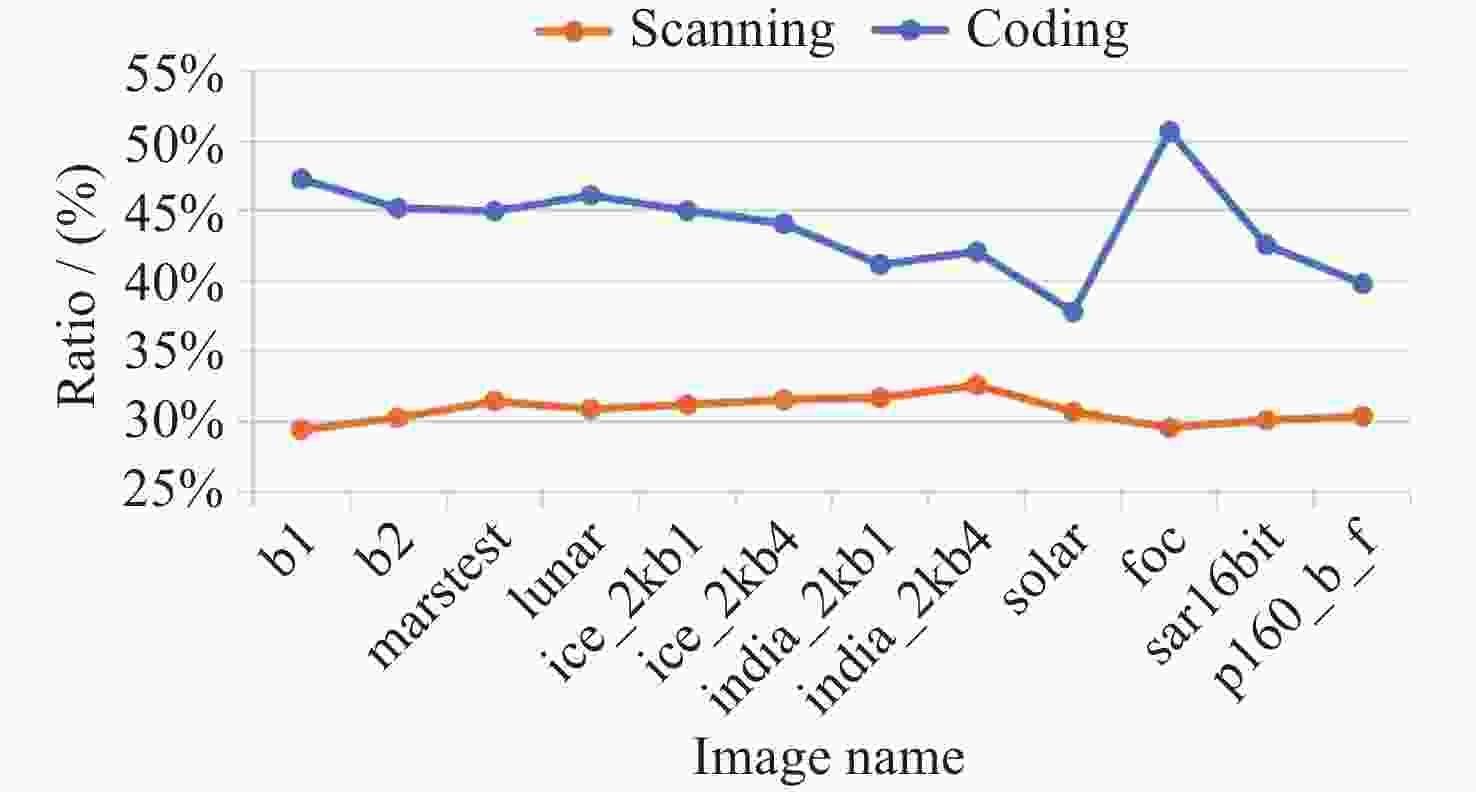

Table 2. Time consumption of segment encoding and throughput for test images

图像名称 位深度/bit 像素数/pixel 段编码耗时/cycle 处理速度/(sample·cycle–1) 200 MHz时的吞吐率

(×106)/(sample·s–1)b1 8 1048576 2399590 0.437 87.40 b2 8 1048576 2393047 0.438 87.64 marstest 8 262144 569853 0.460 92.00 lunar 8 262144 559553 0.468 93.70 ice_2 kb1 10 4194304 9220637 0.455 90.98 ice_2 kb4 10 4194304 8851466 0.474 94.77 india_2 kb1 10 4194304 8934049 0.469 93.89 india_2 kb4 10 4194304 8524784 0.492 98.40 solar 12 1048576 2375073 0.441 88.30 foc 12 524288 1202098 0.436 87.23 sar16 bit 16 262144 602975 0.435 86.95 p160_b_f 16 4194304 9700596 0.432 86.48 -

[1] 张学全. 基于FPGA的星载图像压缩系统实现方法研究[D]. 北京: 中国科学院研究生院(空间科学与应用研究中心), 2009ZHANG Xuequan. Implementation of Onboard Image Compression System Using FPGA[D]. Beijing: Center for Space Science and Applied Research, Chinese Academy of Sciences, 2009 [2] 朱剑冰, 徐勇, 王翠莲, 等. “祝融号”火星车图像压缩软件的设计与实现[J]. 深空探测学报(中英文), 2021, 8(5): 503-510 doi: 10.15982/j.issn.2096-9287.2021.20210065ZHU Jianbin, XU Yong, WANG Cuilian, et al. Image compression software design for Zhurong Mars exploration rover[J]. Journal of Deep Space Exploration, 2021, 8(5): 503-510 doi: 10.15982/j.issn.2096-9287.2021.20210065 [3] CCSDS 122.0-B-1: Image Data Compression[S]. Washington D C: Consultative Committee for Space Data Systems (CCSDS), 2005 [4] KRANITIS N, THEODOROU G, TSIGKANOS A, et al. A reconfigurable FPGA implementation of CCSDS 122.0-B-1 image data compression for ESA PROBA-3 coronagraph system payload[C]//On-Board Payload Data Compression Workshop. Venice: ESA & CNES, 2014 [5] CHANDRAPRABHA K, SHIAK N A, LAKSHMI A, et al. An efficient FPGA implementation of DWT based image data compression system for microsatellites[C]//Proceedings of the 8th International Conference on Advanced Computing and Communication Systems (ICACCS). Coimbatore: Indian Institute of Industrial Engineering (IEEE), 2022 [6] 孙建伟, 张忠伟, 郑铁, 等. 基于FPGA的CCSDS星载数据无损压缩系统设计[J]. 空间科学学报, 2019, 39(5): 694-700 doi: 10.11728/cjss2019.05.694SUN Jianwei, ZHANG Zhongwei, ZHENG Tie, et al. Design of lossless compression system for CCSDS on-board data based on FPGA[J]. Chinese Journal of Space Science, 2019, 39(5): 694-700 doi: 10.11728/cjss2019.05.694 [7] 周文敬, 张学全, 安军社, 等. CCSDS-IDC位平面编码的优化实现[J]. 微电子学与计算机, 2017, 34(9): 32-37 doi: 10.19304/j.cnki.issn1000-7180.2017.09.007ZHOU Wenjing, ZHANG Xuequan, AN Junshe, et al. Optimal implementation of bit plane encoder for CCSDS-IDC[J]. Microelectronics & Computer, 2017, 34(9): 32-37 doi: 10.19304/j.cnki.issn1000-7180.2017.09.007 [8] 胡永刚. CCSDS图像压缩算法位平面编码技术研究及其FPGA实现[D]. 西安: 西安电子科技大学, 2011HU Yonggang. Research on Bit-Plane Encoding of CCSDS Image Compression and Implementation on FPGA[D]. Xi’an: Xidian University, 2011 [9] 孙楠. 机载大尺寸图像压缩系统的设计与实现[D]. 太原: 中北大学, 2024SUN Nan. Design and Realization of Airborne Large Size Image Compression System[D]. Taiyuan: North University of China, 2024 [10] MACHAIRAS E, KRANITIS N. A 13.3 Gbps 9/7M discrete wavelet transform for CCSDS 122.0-B-1 image data compression on a space-grade SRAM FPGA[J]. Electronics, 2020, 9(8): 1234 doi: 10.3390/electronics9081234 [11] 董明岩, 雷杰, 王柯俨, 等. 高效低存储DWT的VLSI结构设计[J]. 西安电子科技大学学报: 自然科学版, 2016, 43(2): 35-40 doi: 10.3969/j.issn.1001-2400.2016.02.007DONG Mingyan, LEI Jie, WANG Keyan, et al. Highly efficient VLSI architecture for DWT with low-storage implementation[J]. Journal of Xidian University, 2016, 43(2): 35-40 doi: 10.3969/j.issn.1001-2400.2016.02.007 [12] JIANG Z C, PAN W D, SHEN H D. Universal Golomb–Rice coding parameter estimation using deep belief networks for hyperspectral image compression[J]. IEEE Journal of Selected Topics in Applied Earth Observations and Remote Sensing, 2018, 11(10): 3830-3840 doi: 10.1109/JSTARS.2018.2864921 [13] SAID A, PEARLMAN W A. A new, fast, and efficient image codec based on set partitioning in hierarchical trees[J]. IEEE Transactions on Circuits and Systems for Video Technology, 1996, 6(3): 243-250 doi: 10.1109/76.499834 -

-

傅志宇 男, 2000年1月出生于重庆市, 现为中国科学院国家空间科学中心硕士研究生, 专业为计算机应用技术, 主要研究方向为星载图像处理. E-mail:

傅志宇 男, 2000年1月出生于重庆市, 现为中国科学院国家空间科学中心硕士研究生, 专业为计算机应用技术, 主要研究方向为星载图像处理. E-mail:

下载:

下载: